台風21号、心配ですね。

「安全を確保するまで出社するな」という無理難題?が会社から出ています。

ある意味福音かもしれません。徒歩なので、安全なんて確保しようがないのですから。どっから何が降ってくるかわかったもんじゃないですからねー。

なので出社しませんでした・・・の屁理屈で通るだろうか、と本気で考えてます。

さて、IBM社のレジストの対訳シリーズが終わりました。

Tradosの練習を兼ねてバイリンガルファイルをエクスポートして訂正してインポートしたりしてたのですが、印刷したものを頭から見ていった時に、「わかっているようでわかっていないこと」だらけなことに気付きました。

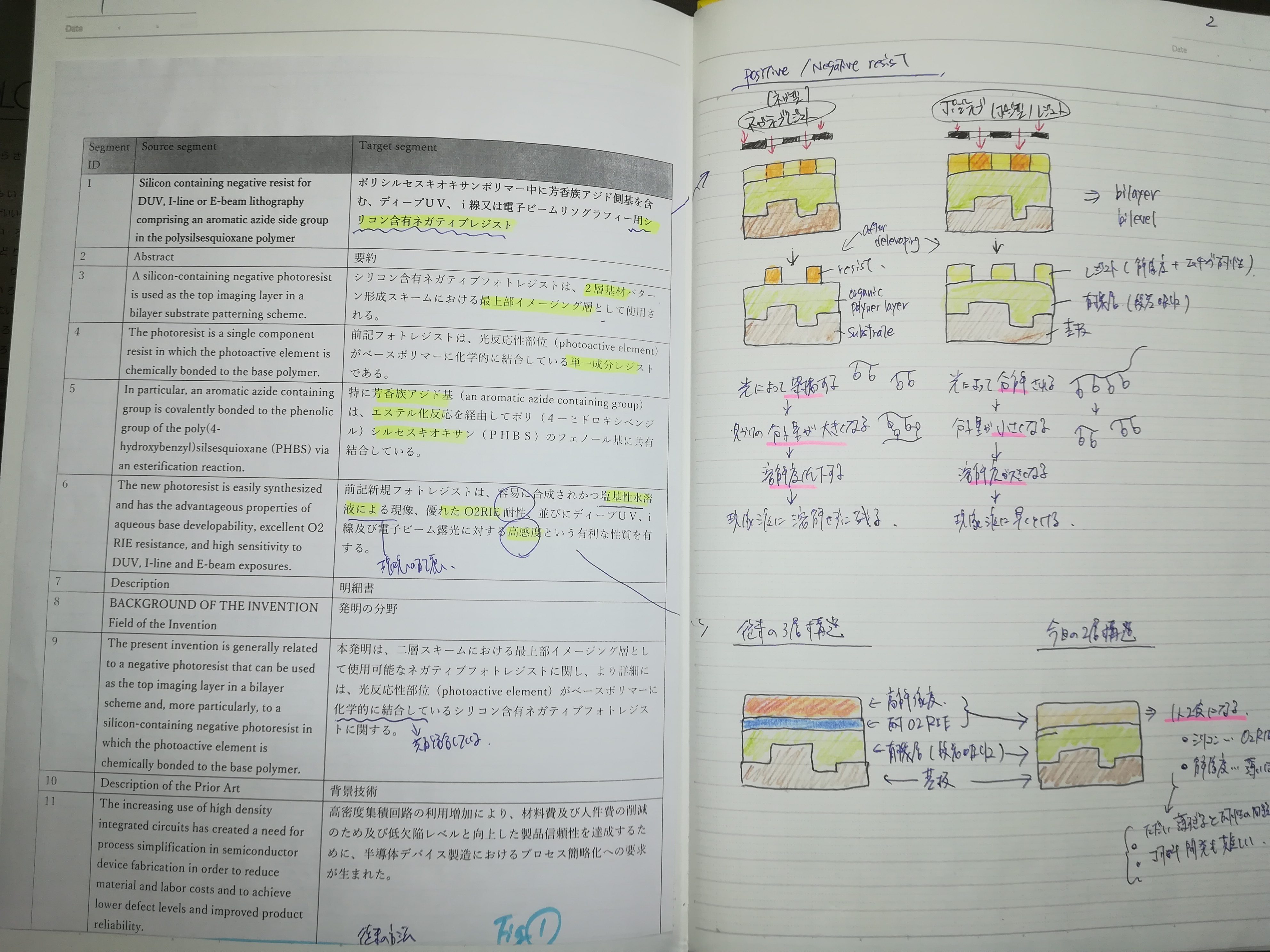

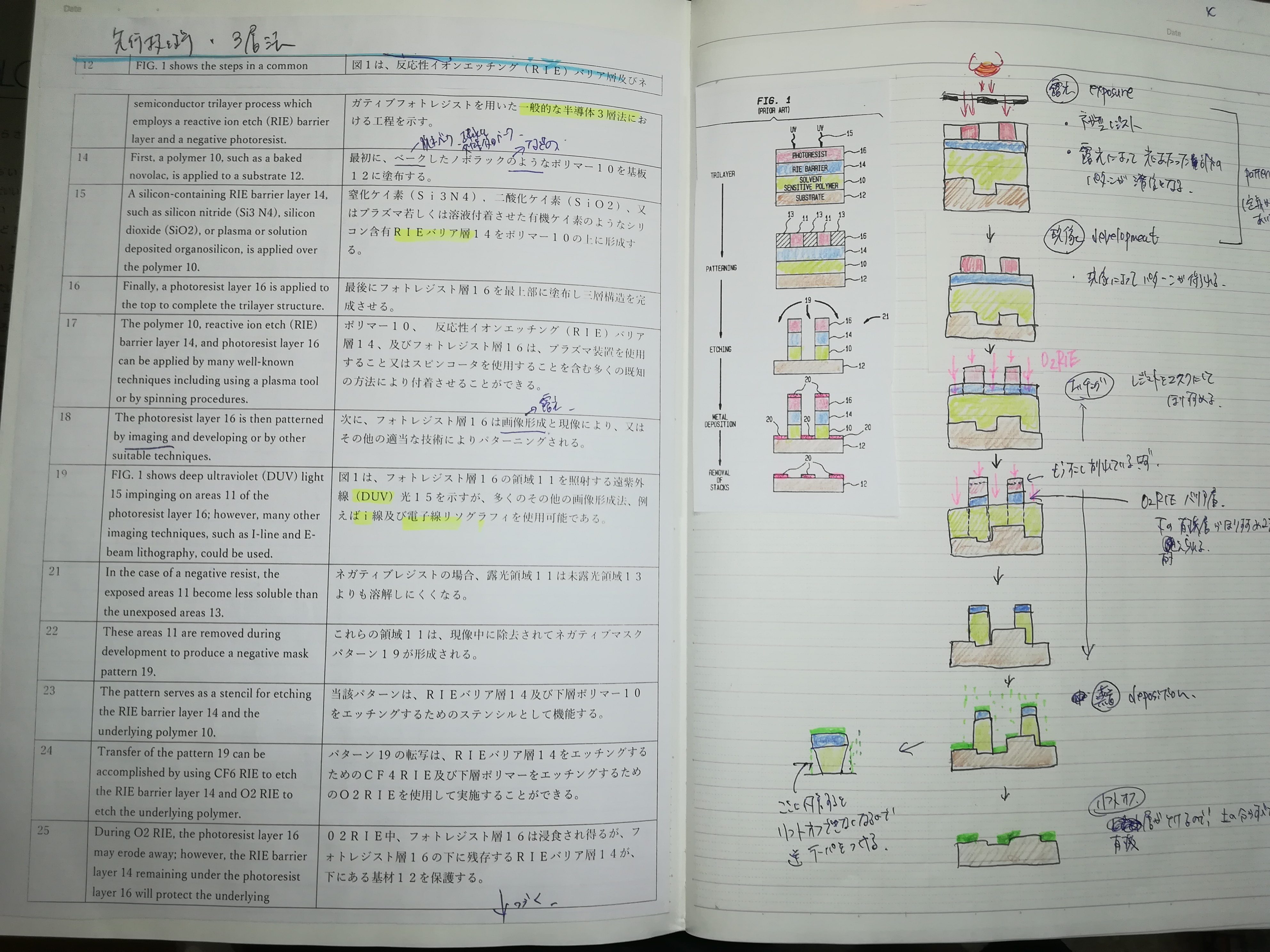

もう一度、図解をしつつ書き込みをしつつ、ノートにまとめていました。

ノートの一部です。

まとめながら、結局この特許ってどこに新規性があるのか、従来技術と比較してどこが優れているのかの観点で整理していなかったことに気付きました。

なので今回、少しその観点からまとめてみたいと思います。

また、これから学習される方、学習中の方には若干のネタバレ要素を含みますのでご注意ください。

今回の特許(US5385804A、特開平6-95385)は、新規のネガ型レジストについての特許です。

要約部分には、「アルカリ現像液での現像が可能で、優れたO2RIE耐性を持ち、さらにディープUV、i線、電子ビーム露光に対して高感度」という有利な性質を持っていることが記載されています。

また背景として、高密度集積回路の利用増加により、コスト削減や歩留まり改善が求められ、半導体製造プロセス簡略化の要求があることが書かれています。

なので、要約部分に記載の有利な性質を持っていることによって、半導体製造プロセスの簡略化につながる、ということですね。

逆に言えば、従来技術には何かしらの改善点があるということになります。

では、従来技術はどのようなものなのでしょうか。

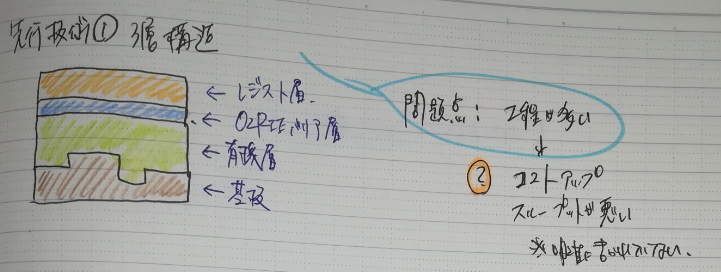

明細書では、次の3つが従来技術として挙げられています。

- 3層構造

- 2層構造(レジスト層をシリル化処理したもの)

- 2層構造(典型的なもの)

3層構造は、下のように文字通り3層になっています(一番下は基板ですので、その上が3層ある、ということです)。ノートからの切り取りで見づらくてすみません。

層が増えればその分工程が増え、工程が増えればコストもかかりますし、不良品が発生する確率も高まります。生産性の問題もあります。

このあたりは明細書には明確に書かれていなかったのですが、「当業者の常識」ということですかね。

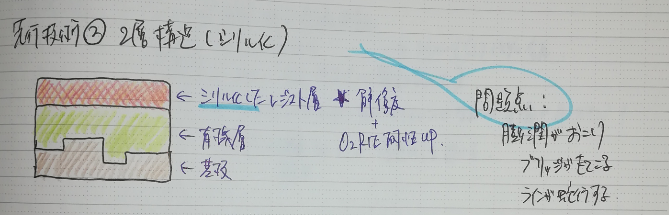

次の2層構造(レジスト層をシリル化処理したもの)です。

2層になりました。1層なくなったから、その分コストも減って時間も減って生産性も向上して良かった良かった・・・となれば良いのですが、話はそう簡単ではありません。

そもそも、もともと2層で良いのならわざわざ3層にしないですもんね。

3層構造にはそれなりの理由があるのです。

では、その理由とは何でしょうか。

それは、

解像度を高める(超微細なパターンをきれいに転写できる)ことと、

感度を高める(反応を早めることで露光時間を短縮し、生産性を上げる)ことを両立させるためです。

3層構造では最上層のレジスト層に解像度の高い材質を用い、その下にドライエッチング耐性のある層を用いてそれぞれの層に「役割分担」させることで、解像度と感度の両立を図ってきました。

ちなみにその下の有機層(ポリマー層)は、基板の段差を吸収し表面を平坦化させるためにあります。

基板にすでにトランジスタなどが組み込まれている場合は表面に凹凸ができるのですが、表面に凹凸がある状態だと露光時に光が乱反射し、必要ない所まで露光されてしまい、パターン形成に影響が出るためです。

話は戻りますが、2層になった場合、1層で解像度とドライエッチング耐性を両立させる必要があります。

そのための方法のひとつが、「シリル化」です。

「シリル化」とはドライエッチング耐性に優れたケイ素をレジスト層のポリマーと化学反応させることによって組み込むことです。

このシリル化したレジスト層が、解像度を高めつつドライエッチング耐性も確保しつつ、と一人二役の活躍をしてくれるわけです。

これでいいじゃん!と言いたいところですが、このプロセスにも欠点がありました。

それは・・・次回に続きます。

・・・いや、あのー、ごめんなさい。

全て書ききる予定でしたが、予想以上に時間がかかってしまったので強制終了です。

ほんと、難しいなー。それでも、書き続けます。

9/2、3(日)の学習記録

学習時間:

9/2(日):14h40m

9/3(月):6h40m

項目: IBM社レジスト特許を読む(71)~ラスト(73)まで

Tradosと格闘する

バイリンガルファイル作成→校正方法について考える

レジスト特許のまとめ(図解)

9/4(火)の学習計画

項目: レジスト特許のまとめ つづき

目標: 2h

項目: 「はじめての半導体プロセス」を読む

目標: 4h30m

メモ:関係する明細書をピックアップしながら読みます。